J-Link PLUS

The JTAG/SWD debug probe with USB interface

Based on a 32-bit RISC CPU, SEGGER's J-Link PLUS can communicate at high speed with the supported target CPUs.

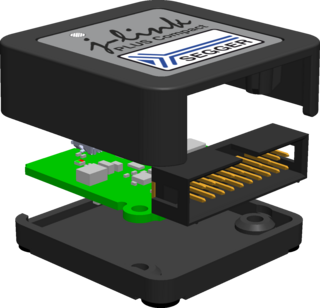

J-Link PLUS is available in two form factors with identical function: J-Link PLUS Classic and J-Link PLUS Compact.

Overview

J-Link PLUS is a USB-powered JTAG debug probe supporting a large number of CPU cores. Based on a 32-bit RISC CPU, it can communicate at high speed with the supported target CPUs. J-Link is used around the world in tens of thousands of places for development and production (flash programming) purposes.

The J-Link debug probes are supported by all major IDEs including Eclipse, GDB-based IDEs and SEGGER Embedded Studio. For a complete list, please refer to supported IDEs. Including all models, more than 500,000 J-Links have been shipped so far, making J-Link probably the most popular debug probe for Arm cores and the de-facto standard.

Key features

- Download speed up to 1 MB/s

- Unlimited breakpoints in flash memory (Flash Breakpoints)

- Use with Ozone, RDI / RDDI and J-Flash

- Built-in VCOM functionality

- Supports a broad range of microcontrollers

- Supports direct download into RAM and flash memory

- Free software updates

Supported devices

The J-Link PLUS as a member of the SEGGER J-Link debug probes supports a wide range of CPU cores. The list of supported manufacturers, families, and devices and SoCs includes tens of thousands of devices in hundreds of device families.

Device not listed? Please don’t hesitate to contact us.

Software

All software is included free of charge. It comes with licenses for all J-Link related SEGGER software products, such as J-Link Unlimited Flash Breakpoints, Ozone, RDI/RDDI, J-Flash, J-Link GDB Server, providing the optimum debugging solution for professional developers.

J-Link PLUS can be used with almost all Arm debuggers, enabling download to flash memory with an unlimited number of breakpoints when debugging programs located in flash memory of most popular Arm microcontrollers. It also comes with the license to use J-Flash, SEGGER's popular flash programming software.

The J-Link Software and Documentation Package is available here:

Multi-platform

As a multi-platform solution, J-Link PLUS comes with the setup and control software for Linux, macOS and Windows. Software and firmware updates are included. Similarly, use on all currently supported target devices, and any that will be added, is also included.

J-Flash

J-Flash is part of the J-Link Software and Documentation Package and allows the programming of the internal and external flash memory of a microcontroller-based embedded system via J-Link.

Flash Breakpoints

The J-Link PLUS comes with an additional feature, called Unlimited Flash Breakpoints. Unlimited Flash Breakpoints allow the user to set an unlimited number of breakpoints when debugging in flash memory.

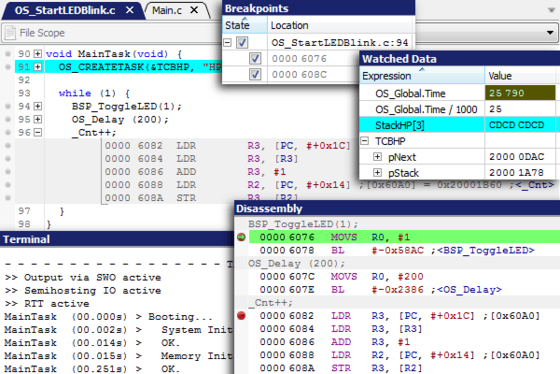

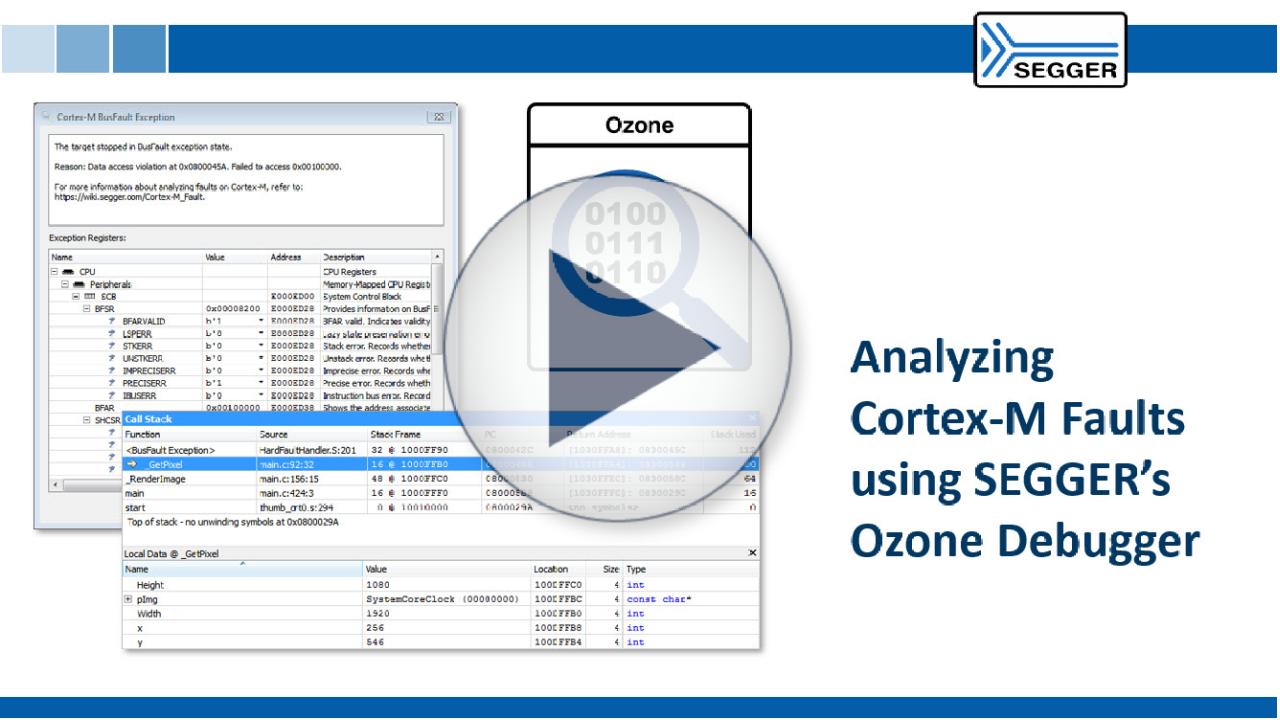

Ozone — The J-Link Debugger

Standalone debugger

Ozone focuses on debugging, with no compiler or project window distractions. All debug windows can be moved, resized and docked, to provide you with the workspace you need.

Ozone offers all well-known debug controls and information windows, and more. Instruction trace, power graph, live watches, and real-time terminal I/O further extend these capabilities.

Performance analyzer

With J-Link's High-Speed Sampling technology, Ozone can sample and visualize an embedded system's variables over time. Checking values and flags in the debugger is easy, while the target keeps running.

J-Link's power measurement features enable you to record the power consumption of your target device in a debug session. This is especially helpful when you develop a low-power device and need to know how power consumption changes when you enable or disable certain components.

Media gallery

Technical specifications

| General | |||||

|---|---|---|---|---|---|

| Supported OS | Microsoft Windows (x86/x64), Linux (x86/x64/Arm), macOS (x86/Apple Silicon) | ||||

| Electromagnetic compatibility (EMC) | EN 55022, EN 55024 | ||||

| Operating temperature | +5°C ... +60°C | ||||

| Storage temperature | -20°C ... +65 °C | ||||

| Relative humidity (non-condensing) | Max. 90% rH | ||||

| Mechanical | |||||

| Size of J-Link PLUS Classic (without cables) | 100mm x 53mm x 27mm | ||||

| Weight of J-Link PLUS Classic (without cables) | 70g | ||||

| Size of J-Link PLUS Compact (without cables) | 46mm x 46mm x 17mm | ||||

| Weight of J-Link PLUS Compact (without cables) | 20g | ||||

| Available Interfaces | |||||

| USB interface (J-Link PLUS Classic) | USB 2.0 (Hi-Speed); USB Type B | ||||

| USB interface (J-Link PLUS Compact) | USB 2.0 (Hi-Speed); USB-C | ||||

| Target interface | JTAG/SWD 20-pin (adapters available) | ||||

| JTAG/SWD Interface, Electrical | |||||

| Power supply | USB-powered Max. 50mA + Target Supply current. | ||||

| Target interface voltage (VIF) | 1.2V ... 5V | ||||

| Current drawn from target voltage sense pin (VTRef) | < 25µA | ||||

| Target supply voltage | 5V (derived from USB voltage) | ||||

| Target supply current | Max. 300mA | ||||

| Reset type | Open drain. Can be pulled low or tristated | ||||

| Reset low level output voltage (VOL) | VOL <= 10% of VIF | ||||

| For the whole target voltage range (1.2V <= VIF <= 5V) | |||||

| LOW level input voltage (VIL) | VIL <= 40% of VIF | ||||

| HIGH level input voltage (VIH) | VIH >= 60% of VIF | ||||

| For 1.2V >= VIF <= 3.6V | |||||

| LOW level output voltage (VOL) with a load of 10 kOhm | VOL <= 20% of VIF | ||||

| HIGH level output voltage (VOH) with a load of 10 kOhm | VOH >= 80% of VIF | ||||

| For 3.6 <= VIF <= 5V | |||||

| LOW level output voltage (VOL) with a load of 10 kOhm | VOL <= 20% of VIF | ||||

| HIGH level output voltage (VOH) with a load of 10 kOhm | VOH >= 80% of VIF | ||||

| JTAG/SWD Interface, Timing | |||||

| Target interface speed | Max. 15 MHz | ||||

| SWO sampling frequency | Max. 30 MHz | ||||

| Data input rise time (Trdi) | Tfdi <= 20ns | ||||

| Data output rise time (Trdo) | Trdo <= 10ns | ||||

| Data output fall time (Tfdo) | Tfdo <= 10ns | ||||

| Clock rise time (Trc) | Trc <= 3ns | ||||

| Clock fall time (Tfc) | Trc <= 3ns | ||||

Assembly dimensions

The compact variant of the J-Link PLUS is designed to mount securely and unobtrusively into development or end user equipment. The small size and two mounting holes enable placing the J-Link PLUS Compact into existing equipment housings or to reserve space for direct-to-PCB mounting.

Typical applications are test fixtures that are used to automate firmware verification during development, or long-term test setups. It also can be used for integrated firmware reflash or service purposes inside end equipment, minimizing the number of tools that service technicians must carry around.

FAQ

Q: Can I use J-Flash with J-Link PLUS?

A: Yes. J-Link PLUS comes with a license for J-Flash preinstalled on the probe itself. No license setup necessary, simply plug in J-Link PLUS and start using J-Flash.

Q: What is the advantage of J-Link versus simple probes such as FTDI-based systems?

A: J-Link has numerous advantages: the actual J-Link software supplied by SEGGER (which enables use with common IDEs), the availability of Unlimited Flash Breakpoints for the debugging of software which runs in the flash of microcontrollers, it’s high speed and it’s simple, fast download into flash memory.

In contrast to most simple probes, J-Link supports adaptive clocking as well as SWD and SWO. It also functions more stably, since it is not just a dump USB to JTAG converter. Instead, it uses the intelligence of the built-in CPU which provides more robust communication. This is especially so in situations where the target CPU runs at low clock speeds.

Q: May I work with more than one J-Link at the same time, on the same machine?

A: Yes, you can connect an unlimited number of J-Links to your PC. No special configuration required; each J-Link is registered with its unique serial number on the PC. This enables you to have multiple J-Links connected at once.

Q: I have multiple Arm cores in my JTAG chain. How can I debug them (simultaneously) with J-Link?

A: That's simple: Two or more debuggers can use the same J-Link simultaneously. Multi-core debugging requires multiple debuggers or multiple instances of the same debugger. You need to tell your debugger which device in the scan chain you want to debug. Additional special settings are not required.

Q: Does J-Link support the Embedded Trace Buffer (ETB)?

A: Yes. J-Link supports ETB on Cortex-M3/M4/M7 and Cortex-A/R (if implemented by target device).

Q: Does J-Link support the Micro Trace Buffer (MTB)?

A: Yes.

Q: Does J-Link support the Embedded Trace Macrocell (ETM)?

A: No. ETM requires another connection to the ARM chip and a CPU with built-in ETM. ETM is supported by the J-Trace product family.